Contratación en el sector electrónico de Guadalajara: por qué 2.000 millones de dólares en inversión no han cerrado la brecha de ingeniería200 millones de USD en exportaciones en 2024 y representó aproximadamente el 35% de la producción electrónica total de [México](/es/mexico-executive-search). El gobierno del estado de Jalisco ha proyectado 2.100 millones de USD en nueva inversión para el período 2025-2026. El empleo directo en el conjunto del sector se situó entre 85.000 y 92.000 trabajadores a finales de 2024. Por cualquier indicador de flujo de capital, el mercado tiene impulso.

Sin embargo, el capital llega más rápido que las personas necesarias para desplegarlo. Las ofertas de empleo para ingenieros electrónicos crecieron un 34% interanual a lo largo de 2024. El tiempo medio de cobertura para puestos especializados se amplió a 68 días, frente a los 52 del año anterior. Y los puestos más críticos en diseño de semiconductores, verificación de hardware e ingeniería de PCB de alta velocidad no se cubren en absoluto a través de canales convencionales. Más del 85% de los ingenieros cualificados en ASIC y diseño físico en este mercado son candidatos pasivos. Están empleados, no buscan activamente y no responden a ofertas publicadas.

Lo que sigue es un análisis sobre el terreno de las fuerzas que están transformando el Manufacturing, los puestos y competencias específicos donde la brecha es más amplia, y lo que los responsables de contratación que compiten por este talento deben comprender antes de comprometerse con planes de crecimiento que dependen de personas que el mercado actualmente no puede proporcionar.

La brecha de despliegue: donde el capital se topa con la restricción

La narrativa del nearshoring ha sido generosa con Guadalajara. La diversificación del riesgo geopolítico, las ventajas de proximidad del USMCA y los costes laborales competitivos han impulsado cifras récord de inversión extranjera directa. Solo en 2024 se anunciaron 1.800 millones de USD en nuevas inversiones en el sector electrónico para Jalisco. La trayectoria ha continuado en 2026, con la agenda de inversión del estado apuntando a 2.100 millones de USD adicionales durante el año en curso.

Pero la inversión anunciada y la capacidad operativa están divergiendo. Solo el 60% de los empleos anunciados se materializó según el calendario previsto a lo largo de 2024, según una comparación de los datos de seguimiento de inversiones de Jalisco con los registros de empleo del IMSS. El 40% restante se estancó o ralentizó, no porque las empresas cambiasen de opinión, sino porque la infraestructura física y humana no podía absorber el capital al ritmo al que llegaba.

Energía y agua: el techo infranqueable

Las restricciones no son abstractas. Guadalajara experimentó 127 horas de cortes de electricidad planificados y no planificados en 2024, frente a las 94 horas del año anterior. Para las instalaciones de pruebas de semiconductores que requieren salas limpias con clima controlado y voltaje estable, cada corte supone daños potenciales a los equipos y pérdida de producción. Las tarifas industriales de CFE aumentaron un 14% interanual, comprimiendo los márgenes de las operaciones intensivas en energía.

La escasez de agua agrava el problema. La zona metropolitana se enfrenta a lo que las autoridades municipales han denominado riesgos de "Día Cero" en un plazo de 18 a 24 meses al ritmo de consumo actual. La fabricación electrónica requiere entre 2,5 y 3,8 metros cúbicos de agua ultrapura por metro cuadrado de silicio procesado. Según informaciones de Reforma citando las directrices de gestión hídrica de SEMI, varios proveedores de EMS han reconsiderado sus planes de expansión intensivos en agua como consecuencia.

Estos no son riesgos que los responsables de contratación puedan ignorar. Un directivo contratado para liderar una instalación de 200 millones de dólares necesita saber si el suministro eléctrico se mantendrá estable. Un director de ingeniería de silicio necesita la garantía de que las operaciones en sala limpia no se verán interrumpidas por el racionamiento municipal de agua. La situación de la infraestructura es inseparable de la adquisición de talento, porque los candidatos más cualificados evalúan ambos aspectos.

Fragilidad de la cadena de suministro

Guadalajara ofrece ventajas logísticas reales. El aeropuerto internacional y la proximidad al puerto de Lázaro Cárdenas proporcionan una conectividad de la que carecen los competidores del interior. Pero los insumos críticos para semiconductores —incluidos sustratos avanzados, productos químicos especializados y fotorresinas— se importan al 100% de Estados Unidos, Taiwán y Alemania. El inventario local cubre habitualmente entre 7 y 14 días de producción, frente a los 45-60 días en los centros de fabricación asiáticos.

Este escaso margen genera vulnerabilidad. Una interrupción en el transporte que causaría un ajuste menor de programación en Penang o Kaohsiung podría paralizar por completo una línea de producción en Guadalajara. Los directores de cadena de suministro en este mercado no gestionan logística: gestionan riesgo con muy poco margen de error. Esa es la razón por la que los líderes experimentados en cadena de suministro exigen primas que reflejan la complejidad del puesto y no la geografía.

8.000 graduados, 78% de escasez: el desajuste cualitativo

Esta es la paradoja central del mercado de talento electrónico de Guadalajara, y la perspectiva que la mayoría de los responsables de contratación ajenos a la región malinterpretan.

Jalisco produce más de 8.000 graduados en ingeniería al año. Solo ITESO contribuye con aproximadamente 480 graduados en mecatrónica e ingeniería electrónica cada curso. La Universidad de Guadalajara añade unos 650 graduados en ingeniería, aunque solo alrededor del 15% se incorpora a campos relacionados con semiconductores. Sobre el papel, la cantera parece adecuada o incluso generosa para un mercado de este tamaño.

Sin embargo, el 78% de los empleadores del sector electrónico en Jalisco declara lo que la encuesta de ManpowerGroup de 2024 clasificó como "dificultad significativa" para cubrir puestos especializados de ingeniería. La desconexión no es un problema de cantidad, sino de planes de estudio.

Los programas universitarios en Jalisco priorizan la ingeniería de software y la ingeniería civil. La formación específica en semiconductores —diseño de señal mixta, metodología de verificación y diseño físico en nodos avanzados— representa menos del 3% de la producción total de ingeniería según las estadísticas de educación en ingeniería de ANFEI de 2024. El mercado no carece de ingenieros. Carece de ingenieros con las competencias específicas que el diseño de semiconductores y la fabricación electrónica avanzada requieren.

Este desajuste es la clave analítica para entender por qué la inversión de capital por sí sola no resolverá el reto de contratación. No se puede contratar a un ingeniero de diseño físico capaz de realizar síntesis de árboles de reloj en 7 nm e inferiores a partir de una cantera de graduados formados principalmente en desarrollo de software. La brecha de competencias no es una cuestión salarial: es una cuestión de formación que requiere años para adquirirse y que las instituciones educativas de Guadalajara no producen a escala suficiente.

La implicación para los responsables de contratación es directa. Cualquier plan de crecimiento que dependa de contratar a más de un puñado de especialistas sénior en semiconductores del mercado local es un plan que depende de la reubicación internacional, la contratación remota o un horizonte temporal más largo de lo que la mayoría de los planes de inversión suponen.

Los puestos que no pueden cubrirse localmente

La gravedad de la escasez varía drásticamente según la función. Los ingenieros de pruebas júnior y los técnicos de fabricación siguen siendo relativamente accesibles, con tasas de candidatura activa en torno al 60% para puestos de pruebas de nivel inicial y alta movilidad entre el personal de producción en instalaciones operadas por Flex, Jabil y Sanmina. El problema se concentra en los niveles especializado y directivo.

ASIC y diseño físico

Los ingenieros sénior de diseño físico con experiencia en 7 nm e inferiores son el perfil más escaso del mercado. La búsqueda de un ingeniero de diseño físico para el desarrollo de SoC en 5 nm por parte de un proveedor EMS de Nivel 1, documentada en los expedientes de la agencia estatal de empleo de Jalisco, permaneció abierta durante 11 meses antes de cubrirse mediante una reubicación internacional desde Bangalore. El puesto requería competencia bilingüe y dominio de las herramientas de Synopsys y Cadence. Menos del 15% de los insumos de la lista de materiales se obtiene localmente para electrónica compleja, y una proporción similar se aplica, aproximadamente, a la disponibilidad de ingenieros capaces de diseñar lo que se monta en esas placas.

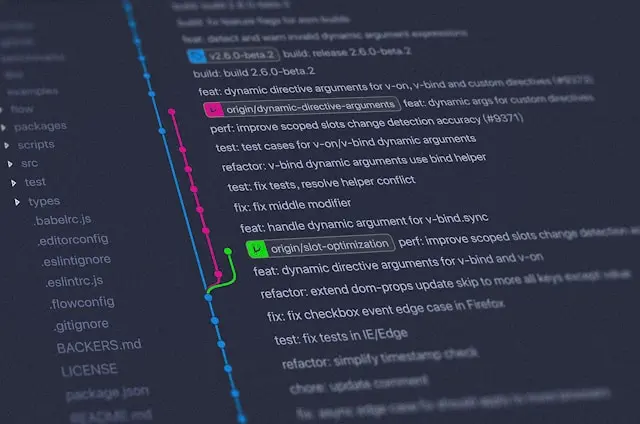

Más del 85% de los ingenieros cualificados en ASIC y diseño físico en Guadalajara son candidatos pasivos, según datos de LinkedIn Talent Solutions de 2024. No se presentan a ofertas. No consultan portales de empleo. Deben ser localizados mediante métodos de búsqueda directa y específica que lleguen a candidatos que no tienen intención de buscar hasta que la oportunidad adecuada les encuentra de forma inesperada.

Ingeniería de verificación

Los ingenieros de verificación de hardware con experiencia en SystemVerilog y UVM representan la segunda escasez más aguda. La antigüedad media en el puesto actual es de 4,2 años. Las tasas de candidatura espontánea se sitúan por debajo del 5% del total de contrataciones. La proporción de candidatos pasivos entre los responsables sénior de verificación refleja la del mercado general de diseño de semiconductores: abrumadoramente invisible para los métodos de contratación convencionales.

Informaciones del sector publicadas por El Economista en diciembre de 2024 describieron una rotación notable en el Centro de Diseño de Intel en Guadalajara durante el segundo semestre de ese año. Según la publicación, ingenieros de verificación fueron captados por centros de diseño competidores en Austin, Texas, y Querétaro, México, con primas salariales del 35 al 45% por encima de las bandas retributivas locales de Intel. Que una empresa de la envergadura y el reconocimiento de marca de Intel no pudiera retener a estos ingenieros con los niveles de compensación existentes dice a los responsables de contratación todo lo que necesitan saber sobre la intensidad competitiva en este segmento.

Liderazgo de operaciones EMS

En el nivel ejecutivo, la restricción adopta una forma diferente. Los directores de planta y VP de operaciones para instalaciones con 3.000 o más empleados se cubren en el 70% de los casos a través de redes de referencia y caza de talentos. La proporción de candidatos pasivos frente a activos es de nueve a uno. El grupo de líderes que han gestionado instalaciones con ingresos de 200 millones de dólares en un mercado con la combinación específica de inestabilidad energética, escasez hídrica, fragilidad de cadena de suministro y costes de seguridad de Guadalajara es intrínsecamente reducido. No se trata de competencias transferibles desde un entorno de fabricación estable y bien dotado de recursos: requieren un criterio operativo forjado bajo restricciones que la mayoría de los centros de fabricación globales no imponen.

Compensación: la prima del 35% que aun así pierde talento

La estructura retributiva de Guadalajara para puestos de semiconductores refleja la escasez, pero también revela la vulnerabilidad fundamental de retención del mercado.

Los ingenieros Sénior de diseño ASIC con siete o más años de experiencia perciben salarios base de 2,8 a 3,6 millones de MXN anuales, equivalentes a aproximadamente 140.000-180.000 USD. En multinacionales, la participación en capital y las unidades de acciones añaden una prima del 25 al 35% sobre el salario base. Los ingenieros sénior de verificación se sitúan ligeramente por debajo, entre 2,5 y 3,2 millones de MXN de base. Estas cifras ya representan una prima del 20 al 30% sobre los puestos generales de IT e ingeniería de software en la misma ciudad, según el informe de talento de ingeniería de PageGroup de 2024.

En el nivel ejecutivo, las cifras ascienden considerablemente. Los VP de ingeniería en diseño de semiconductores perciben entre 5,5 y 8,0 millones de MXN anuales, con bonificaciones por rendimiento del 40 al 60% del salario base. Los directores de planta de grandes operaciones EMS alcanzan paquetes retributivos totales de 12 a 15 millones de MXN, es decir, entre 600.000 y 750.000 USD incluyendo bonificaciones. No son salarios de mercado emergente. Son paquetes competitivos a escala global.

Y aun así no bastan para evitar la fuga hacia centros de Estados Unidos. Los ingenieros con ocho o más años de experiencia que se trasladan a Austin o Phoenix reciben multiplicadores salariales de 3,5x a 4x en términos de dólares estadounidenses. Incluso Querétaro, competidor nacional, ofrece una compensación entre un 10 y un 15% superior para puestos híbridos de aeroespacial-electrónica, junto con una fiabilidad de infraestructura sustancialmente mejor. Los ingenieros que se marchan no lo hacen porque Guadalajara pague poco según los estándares locales. Se marchan porque el mercado global valora sus competencias a un nivel que el mercado local no puede sostener.

Esta es la dinámica retributiva que el análisis comparativo de mercado debe contemplar en este entorno. Un paquete que parece competitivo frente a la media de Guadalajara resulta irrelevante si la alternativa del candidato es Austin a cuatro veces el salario base. La referencia pertinente no es local, sino internacional, y la brecha se amplía más rápidamente precisamente en el nivel de responsabilidad donde se sitúan los puestos más críticos.

Geografía competitiva: quién está atrayendo el talento

Guadalajara no compite de forma aislada. El talento que necesita es demandado simultáneamente por múltiples mercados, cada uno con ventajas diferenciadas.

Querétaro ha emergido como el competidor nacional más relevante. La cantera de la Universidad Aeronáutica en Querétaro alimenta directamente puestos híbridos de aeroespacial-electrónica, atrayendo talento que de otro modo podría incorporarse a las funciones de electrónica automotriz de Guadalajara. Querétaro ofrece mejor fiabilidad de infraestructura y una compensación moderadamente superior. Está lo suficientemente cerca geográficamente como para que un traslado se perciba como un paso incremental y no como un cambio de vida, lo que reduce la barrera para los candidatos que evalúan una transición.

Austin y Phoenix representan una categoría de competencia completamente diferente. No son mercados con los que Guadalajara pueda equipararse en compensación. El multiplicador salarial de 3,5x a 4x en términos de USD, combinado con la flexibilidad del trabajo remoto y las ventajas percibidas en calidad de vida, genera una atracción que ningún empleador de Guadalajara puede contrarrestar solo con dinero. La respuesta debe provenir del alcance del puesto, la trayectoria profesional y los retos técnicos específicos disponibles en los centros de diseño de Guadalajara.

Tijuana compite por ejecutivos bilingües de fabricación con una prima del 8 al 12% sobre Guadalajara, impulsada por la proximidad a los equipos de diseño de California. San José de Costa Rica compite por puestos de servicios compartidos y centros de diseño, ofreciendo una infraestructura de idioma inglés más consolidada y, de forma decisiva, un perfil de estabilidad política y seguridad que Guadalajara tiene dificultades para igualar. Los gastos en seguridad privada para instalaciones electrónicas en Guadalajara promedian el 2,3% de los presupuestos operativos, frente al 0,8% en Costa Rica y el 0,4% en instalaciones equivalentes de Estados Unidos, según la encuesta de clima empresarial de 2024 de la American Chamber of Commerce of Mexico.

El panorama competitivo añade una capa de urgencia a cada búsqueda. Un candidato identificado para un puesto en Guadalajara es simultáneamente visible para empleadores en al menos tres mercados competidores. La velocidad de contacto no es una preferencia: es un factor determinante de si el candidato seguirá disponible cuando llegue la oferta.

Riesgos regulatorios y comerciales que reconfiguran la ecuación del talento

La revisión del USMCA en 2026 introduce una incertidumbre que afecta a cada decisión de contratación en este mercado. Los aranceles propuestos del 25% sobre productos mexicanos —tema recurrente en la retórica comercial de Estados Unidos desde finales de 2024— eliminarían la ventaja de costes de Guadalajara para las exportaciones de electrónica de consumo de llegar a implementarse. Los requisitos actuales de reglas de origen ya penalizan las operaciones de semiconductores de la ciudad: la difusión de obleas debe realizarse dentro del territorio del USMCA, y Guadalajara carece de instalaciones de fabricación de obleas.

La reforma de subcontratación de México de 2023-2024 ha incrementado los costes de empleo directo entre un 12 y un 18% para las empresas EMS que anteriormente dependían de subcontratistas especializados. Esta reforma fue diseñada para mejorar la protección de los trabajadores, pero su efecto práctico en el sector electrónico ha sido elevar el suelo de costes para cada contratación. Las empresas que antes gestionaban plantillas especializadas a través de terceros ahora las incorporan directamente, con todas las prestaciones y obligaciones de cumplimiento asociadas.

Los nuevos requisitos de localización de datos añaden una complicación adicional. Las enmiendas a las normas de protección de datos exigen que ciertos datos de diseño de semiconductores permanezcan en servidores mexicanos, lo que interrumpe los flujos de trabajo de automatización del diseño electrónico (EDA) basados en la nube de los que dependen muchos centros de diseño. Para un VP de ingeniería que evalúa Guadalajara frente a Austin o Penang, la imposibilidad de utilizar libremente herramientas EDA en la nube no es un inconveniente menor: es una restricción sobre cómo se realiza el trabajo.

Estos factores regulatorios no eliminan el atractivo de Guadalajara, pero cambian el perfil del líder necesario para gestionar operaciones aquí. El director de planta que este mercado necesita no es solo un experto en operaciones: debe comprender el cumplimiento del T-MEC, las estrategias de dual-shoringcom/es/article-non-compete-clauses) y el entorno regulatorio de un mercado donde las reglas están cambiando activamente. Esto reduce aún más la cantera de candidatos, porque la intersección entre liderazgo en fabricación y experiencia en política comercial es intrínsecamente reducida.

Qué significa esto para los responsables de contratación en 2026

La conclusión que emerge de estos datos no trata sobre escasez, sino sobre suposiciones erróneas respecto a la escalabilidad. El capital ha llegado a Guadalajara más rápido de lo que la infraestructura humana y física puede absorber. El resultado es un mercado donde las cifras de inversión anunciadas sugieren un auge, pero la experiencia real de contratación revela un cuello de botella: la tasa de materialización de empleo del 60%, la vacante de 11 meses para un ingeniero de diseño, los 68 días de media para cubrir puestos especializados. El sector electrónico de Guadalajara no está limitado por la demanda ni por el capital. Está limitado por la suposición de que ambos pueden escalar de forma lineal en un mercado donde la energía, el agua, las canteras formativas y la oferta de talento imponen límites no lineales.

Para las organizaciones que construyen o amplían operaciones en este mercado, tres realidades deben informar el enfoque de la contratación ejecutiva y de especialistas.

En primer lugar, la captación exclusivamente local no cubrirá los puestos de diseño y verificación de semiconductores. La cantera educativa produce menos del 3% de graduados con la especialización pertinente. Cualquier plan de contratación para estas funciones debe incluir reubicación internacional, contratación remota estructurada o un horizonte de inversión en formación medido en años y no en trimestres.

En segundo lugar, la competencia por el talento sénior existente en Guadalajara es internacional, no local. El marco de comparación relevante para un ingeniero sénior de verificación no son otros empleadores de Guadalajara, sino Austin, Phoenix y Querétaro. Los paquetes retributivos deben diseñarse frente a ese marco competitivo, y la propuesta total —incluyendo el alcance del puesto y la trayectoria profesional— debe ofrecer algo que esos mercados competidores no puedan igualar.

En tercer lugar, los riesgos de infraestructura son reales y deben comunicarse a los candidatos durante el proceso de selección, no descubrirse después. Los candidatos pasivos más cualificados evaluarán la fiabilidad energética, la seguridad hídrica y los costes de seguridad junto con el salario. La transparencia sobre estas limitaciones, acompañada de un plan de mitigación creíble, resulta más persuasiva que una prima salarial ofrecida sin contexto.

Para las organizaciones que compiten por liderazgo en diseño de semiconductores, verificación y operaciones EMS en Guadalajara —donde más del 85% de los candidatos cualificados no son visibles en ningún portal de empleo y los retos de infraestructura requieren líderes con un perfil operativo muy específico—, contacte con nuestro equipo de Executive Search para conocer cómo KiTalent aborda este mercado. Con AI y Tecnología que identifica candidatos pasivos en geografías competidoras y un modelo de pago por entrevista que elimina el riesgo de retainer inicial, KiTalent presenta candidatos directivos listos para entrevista en un plazo de 7 a 10 días. Nuestra tasa de retención del 96% a un año refleja la precisión de emparejar candidatos no solo con puestos, sino con las condiciones operativas específicas de los mercados que liderarán.

Preguntas frecuentes

¿Cuál es el tiempo medio de cobertura para puestos de ingeniería electrónica en Guadalajara?

A finales de 2024, el tiempo medio de cobertura para puestos especializados de ingeniería electrónica en Guadalajara se amplió a 68 días, frente a los 52 días de 2023. Los puestos sénior de diseño de semiconductores —en particular los de diseño físico de ASIC y verificación de hardware— requieren plazos considerablemente más largos. Un caso documentado con un puesto de diseño físico de SoC en 5 nm tardó 11 meses en cubrirse. Para puestos directivos como directores de planta EMS, la búsqueda depende habitualmente de métodos directos de headhunting y Executive Search en lugar de canteras de candidatos activos, dada una proporción de candidatos pasivos frente a activos de nueve a uno.

¿Por qué existe escasez de talento en el sector electrónico de Guadalajara a pesar del gran número de graduados en ingeniería?Jalisco produce más de 8.000 graduados en ingeniería al año, pero la escasez es cualitativa y no cuantitativa. La formación específica en semiconductores en áreas como diseño de señal mixta, metodología de verificación y diseño físico en nodos avanzados representa menos del 3% de la producción total de ingeniería de las universidades de la región. La mayoría de los graduados se especializan en software o ingeniería civil. El resultado es un mercado donde la oferta agregada parece suficiente pero las competencias específicas requeridas por el diseño de semiconductores y la fabricación electrónica avanzada siguen siendo extremadamente escasas.

¿Cuánto ganan los ingenieros sénior de electrónica y semiconductores en Guadalajara?Los ingenieros sénior de diseño ASIC con siete o más años de experiencia perciben salarios base de aproximadamente 2,8 a 3,6 millones de MXN anuales, equivalentes a 140.000-180.000 USD. La participación en capital en multinacionales añade entre un 25 y un 35% adicional. En el nivel de VP de ingeniería, la compensación total incluyendo bonificaciones oscila entre 5,5 y 8,0 millones de MXN. Los directores de planta EMS que gestionan instalaciones con 3.000 o más empleados pueden alcanzar paquetes totales de 12 a 15 millones de MXN. Estos puestos conllevan una prima del 20 al 30% sobre los puestos comparables de ingeniería de software en la misma ciudad.

¿Cómo se compara Guadalajara con otras ciudades en talento electrónico y de semiconductores?El principal competidor nacional de Guadalajara es Querétaro, que ofrece una compensación entre un 10 y un 15% superior para puestos de aeroespacial-electrónica y mejor fiabilidad de infraestructura. A nivel internacional, Austin y Phoenix atraen a ingenieros sénior con multiplicadores salariales de 3,5x a 4x en términos de USD. Tijuana compite por ejecutivos bilingües de fabricación con una prima salarial del 8 al 12%. Costa Rica compite por puestos de centros de diseño con una infraestructura de idioma inglés más consolidada y menores costes de seguridad. La ventaja de Guadalajara reside en su concentración de operaciones EMS y su posición como único centro de diseño de Intel en América Latina.

¿Cómo pueden las empresas encontrar talento pasivo de ingeniería de semiconductores en Guadalajara?

Más del 85% de los ingenieros cualificados en ASIC y diseño físico en Guadalajara son candidatos pasivos que están empleados y no buscan activamente nuevos puestos. Las tasas de candidatura espontánea para responsables sénior de verificación se sitúan por debajo del 5% del total de contrataciones. La publicidad convencional de empleo solo alcanza a una fracción de la cantera disponible. KiTalent utiliza Mapeo de Talento potenciado por AI para identificar y contactar a estos candidatos en Guadalajara y geografías competidoras, presentando listas cortas de candidatos listos para entrevista en un plazo de 7 a 10 días mediante un modelo de pago por entrevista que elimina los compromisos de retainer inicial.

¿Qué riesgos de infraestructura afectan a la expansión de la fabricación electrónica en Guadalajara?

Guadalajara se enfrenta a tres restricciones materiales de infraestructura. La fiabilidad energética se deterioró en 2024, con 127 horas de cortes frente a las 94 del año anterior, lo que plantea riesgos particulares para las operaciones en sala limpia. La escasez de agua se aproxima a niveles críticos, con las autoridades municipales proyectando riesgos de "Día Cero" en un plazo de 18 a 24 meses al ritmo de consumo actual. Los márgenes de la cadena de suministro son reducidos, con un inventario local de insumos críticos para semiconductores que cubre solo entre 7 y 14 días de producción frente a los 45-60 días en los centros asiáticos. Estas restricciones son una razón clave por la que solo el 60% de la inversión anunciada se tradujo en empleos según el calendario previsto a lo largo de 2024.